# EE 505

Lecture 16

**Current Steering DACs**

Review from Last Lecture R-String DAC

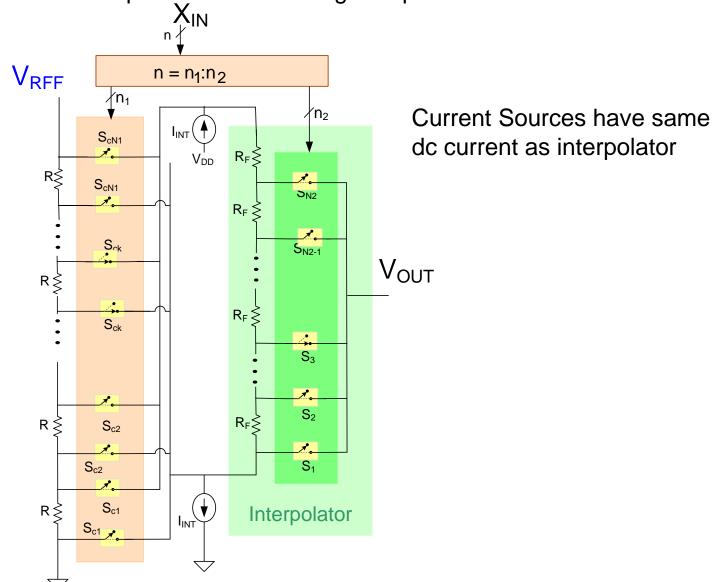

Compensated Fine String Interpolator

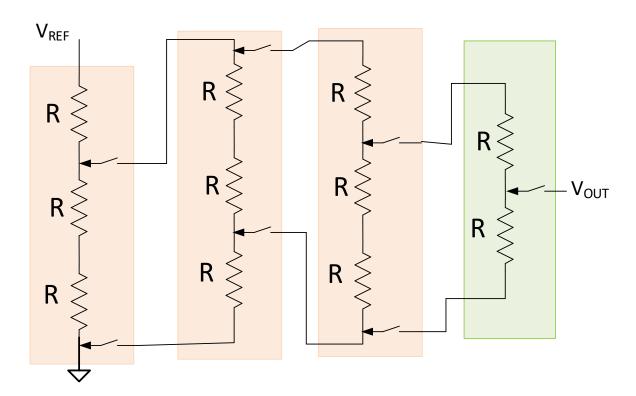

# Review from Last Lecture Kelvin-Varley Divider

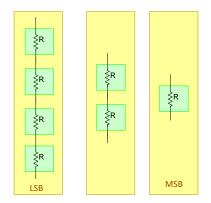

#### Concept Can Be Extended to Any Base

- Shown as binary divider (1 bits/stage)

- 3 resistors in each string except last which has 2

No decoder needed to control switches

**Review from Last Lecture**

## Kelvin-Varley Divider

#### Concept Can Be Extended to Any Base

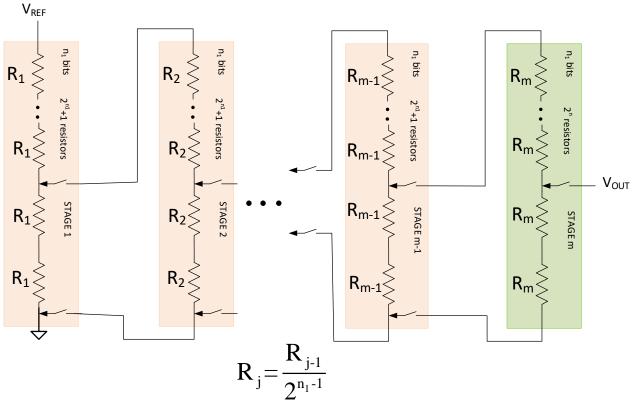

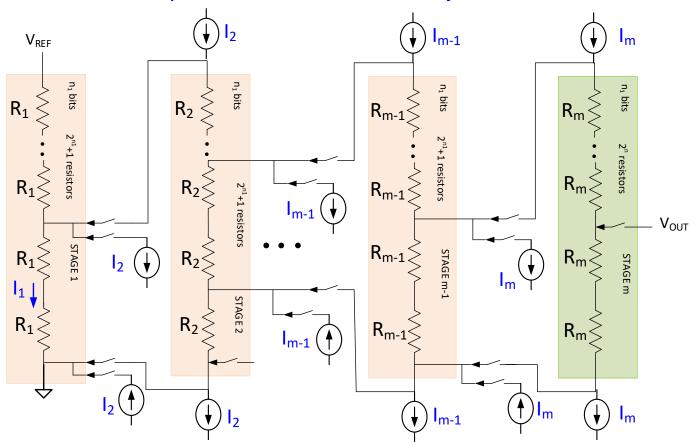

- ➤ Shown as binary divider (n₁ bits/stage)

- 2<sup>n1</sup>+1 resistors in each string except last which has 2<sup>n1</sup>

Small decoder needed to control switches

Voltage on MSB nodes ideally do not change with code

Switch impedance affects attenuation

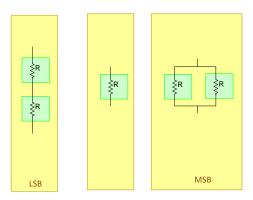

## Kelvin-Varley Divider

#### Concept Can Be Extended to Any Base

- ➤ Shown as binary divider (n₁ bits/stage)

- > 2<sup>n1</sup>+1 resistors in each string except last which has 2<sup>n1</sup>

$$I_i = I_1$$

for all i

Switch impedance compensation

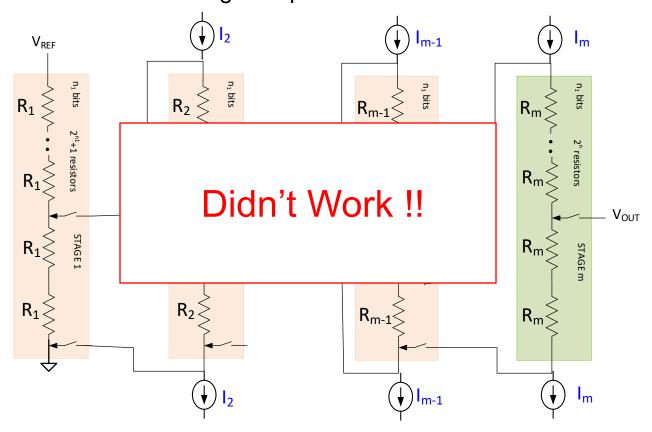

## Kelvin-Varley Divider

Concept Can Be Extended to Any Base

$$I_i = I_1$$

for all i

Switch impedance compensation

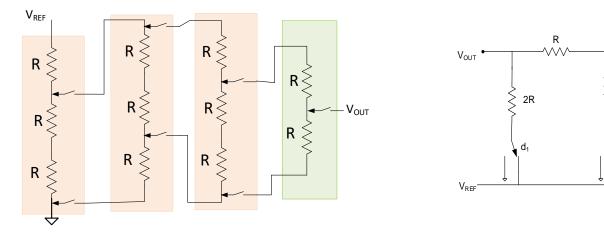

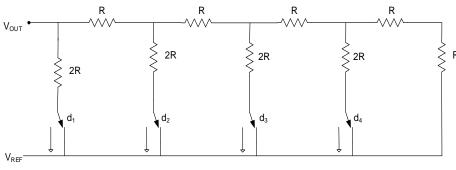

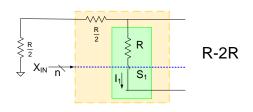

### Comparison of Kelvin-Varley and R-2R

Kelvin-Varley Divider

R-2R

Both have 3 Resistors and 2 switches / slice

Are there any benefits of the KV structure relative to the R-2R structure?

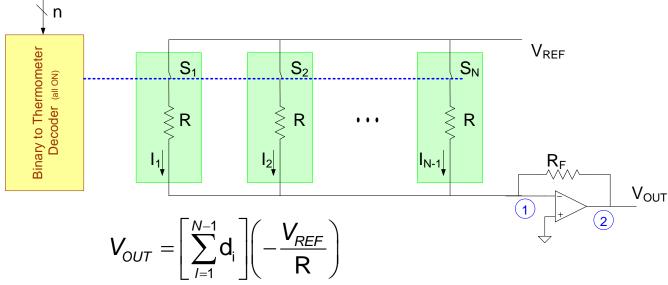

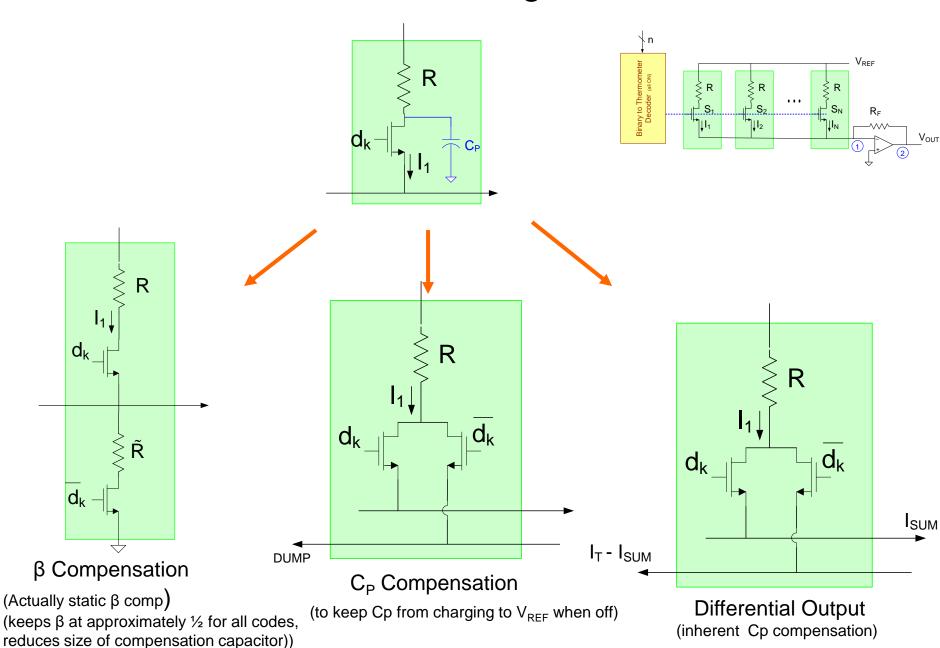

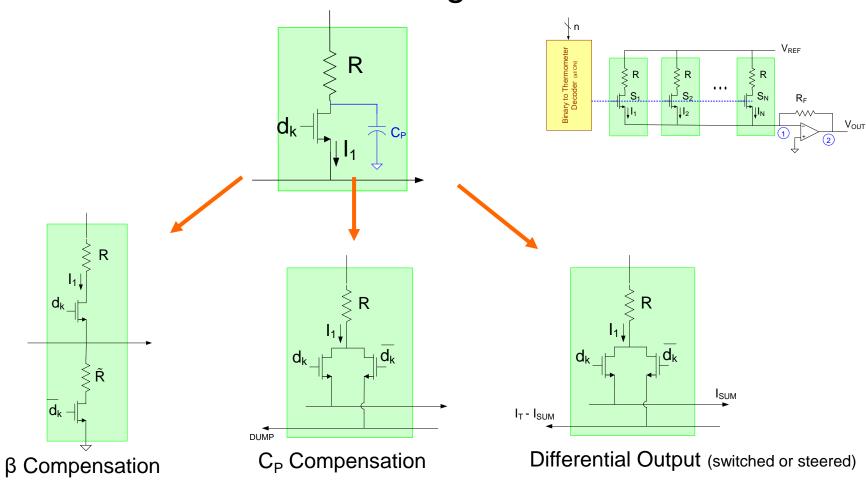

$$d_k = \begin{cases} 1 & \text{if } S_k \text{ closed} \\ 0 & \text{if } S_k \text{ open} \end{cases}$$

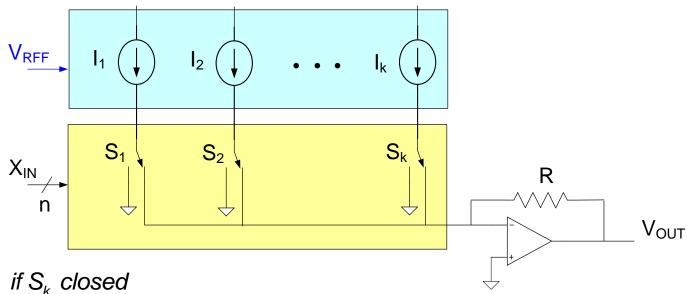

$$V_{OUT} = \left[\sum_{i=1}^{k} d_{i} I_{i}\right] (-R)$$

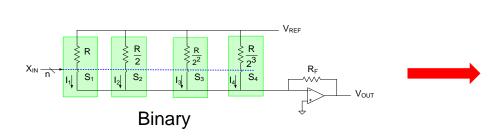

- Current sources usually unary or binary-bundled unary

- Termed bottom-plate switching

- Can eliminate resistors from DAC core

- Op Amp and resistor R can be external

- Can use all same type of switches

- Switch impedance not critical nor is switch matching

- Popular MDAC approach

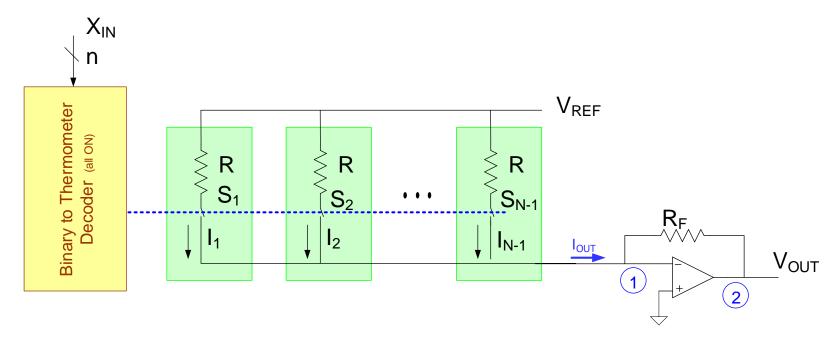

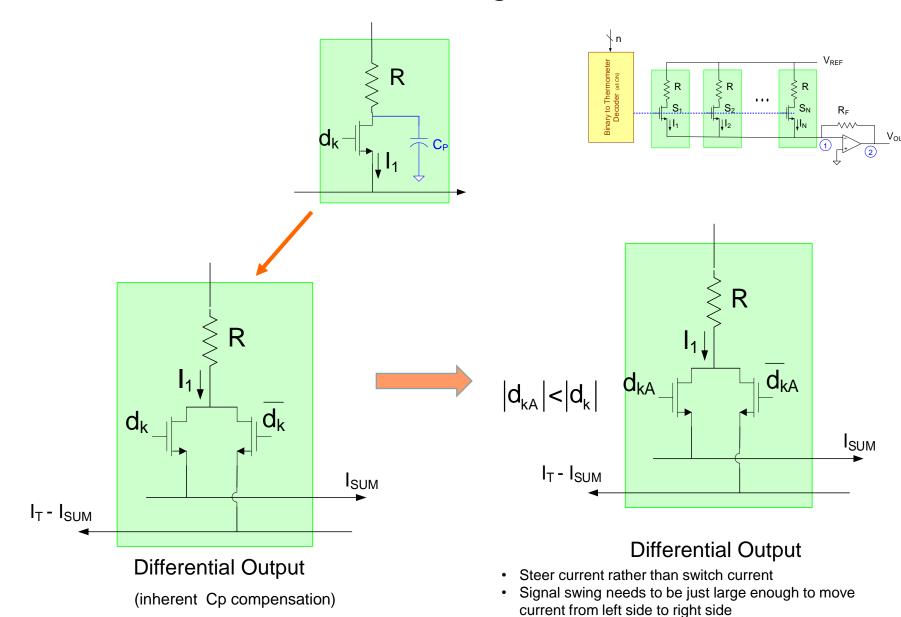

#### **Unary Current Sources**

## Inherently Insensitive to Nonlinearities and Component Values in Switches and Resistors

- Termed "top plate switching"

- Thermometer coding (routing challenge!)

- Excellent DNL properties

- INL may be poor, typically near mid range

- Switch kickback to V<sub>REF</sub>

- Not suitable for use as MDAC

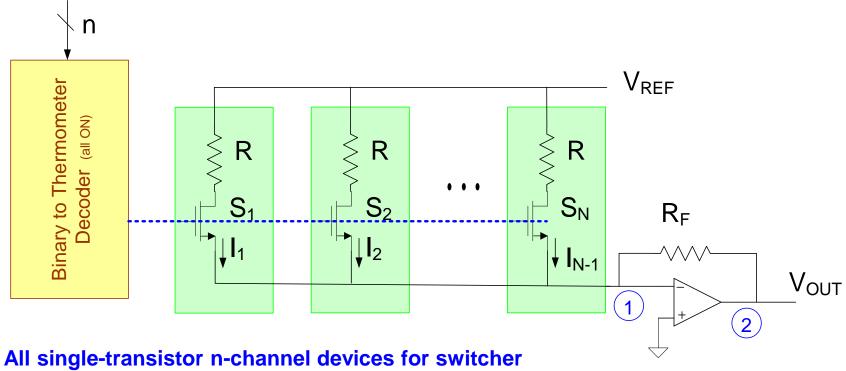

#### **Unary Current Sources**

- Inherently Insensitive to Nonlinearities in Switches and Resistors

- Smaller ON resistance and less phase-shift from clock edges

- Termed "bottom plate switching"

- Thermometer coded

- Can be used as MDAC

- Reduced kickback to V<sub>RFF</sub>

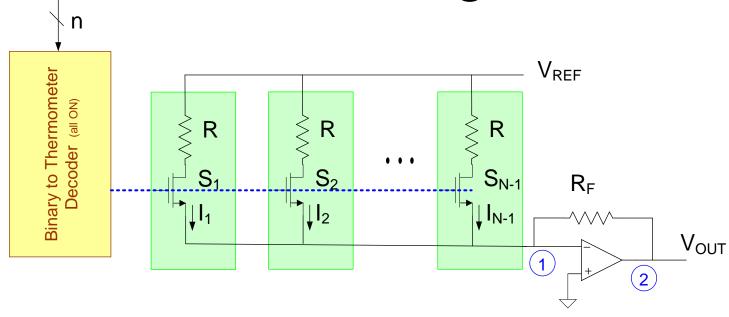

- **Unary R:switch cells**

- Parasitic capacitances on drain nodes of switches cause transient settling delays

- R+Rsw is nonlinear (so nonlinear relationship between  $I_k$  and  $V_{REF}$ ) but does not affect linearity of DAC

- Resistor and switch impedance matching important (but not to each other)

- Previous code dependent transient (parasitic capacitances on drains of switches)

**Transistor Implementation of Switches**

$$\beta = \frac{\frac{R_{CELL}}{k}}{\frac{R_{CELL}}{k} + R_F} = \frac{R_{CELL}}{R_{CELL} + kR_F}$$

If  $V_{OUTFS} = -V_{REF} \frac{N-1}{N}$

$$\frac{N}{2N-1} < \beta \le 1$$

approximate

$\frac{1}{N-1} < \beta \le 1$  approximately  $0.5 < \beta \le 1$

R<sub>CELL</sub>=N R<sub>F</sub>

Phase-margin code dependent so distortion will be introduced if not fully settled Current drawn from  $V_{REF}$  changes with code (settling issues if  $R_{0\ VREF}$  is not 0)

Will  $\beta$  compensation "half" resistance of cells? Will  $\beta$  compensation double area for cells?

Is matching of R and compensating R critical?

Can  $C_p$  and  $\beta$  compensation be used simultaneously? Is the frequency-dependent  $\beta$  code dependent?

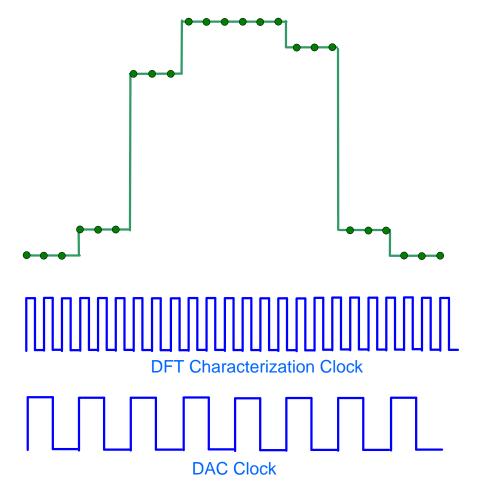

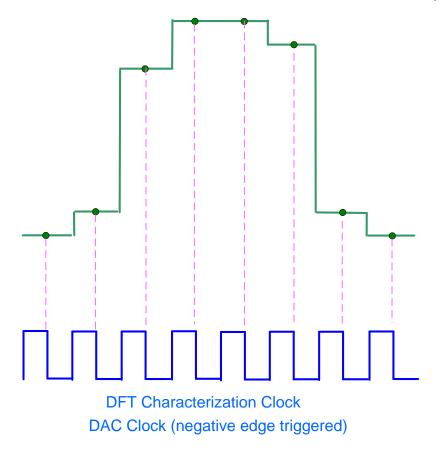

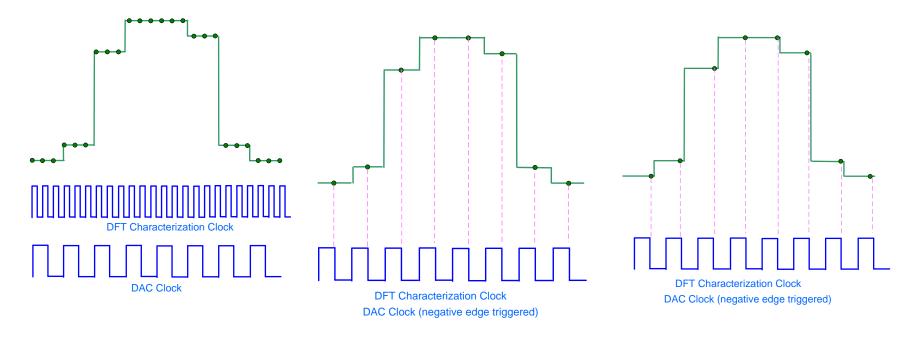

many more samples per DAC clock are often used (e.g. 64K samples, 31 periods would be approx 2114 samples/period)

Is this how we should characterize the spectral performance of a DAC?

one mid-period sample per DAC clock period (or maybe even less)

Assume Nyquist sampling rate is satisfied

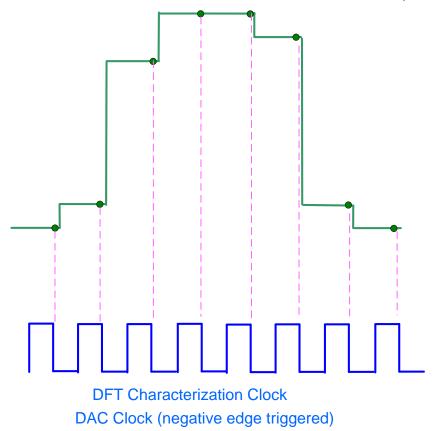

Is this how we should characterize the spectral performance of a DAC?

one near-end sample per DAC clock period

Assume Nyquist sampling rate is satisfied

Is this how we should characterize the spectral performance of a DAC?

Assume Nyquist sampling rate is satisfied

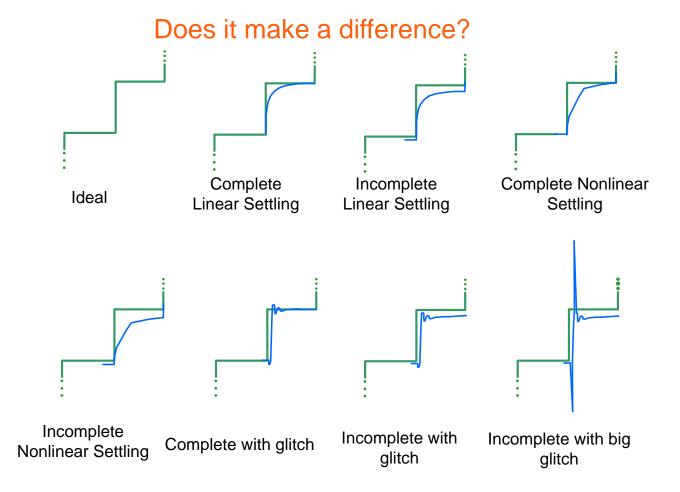

Does it make a difference?

Yes! But depends on application which is useful

Yes! But depends on application which is useful

- If entire DAC output is of interest, any nonlinearity including previous code dependence will degrade linearity

- If DAC output is simply sampled, only value at sample point is of concern

#### **Current Steering**

- Unary cells bundled to implement binary cells (so no net change in number of cells)

- Need for decoder eliminated!

- DNL may be a major problem

- INL performance about same as thermometer coded if same unit resistors used

- Sizing and layout of switches is critical

- Large total resistance

Observe thermometer coding and binary weighted both offer some major advantages and some major limitations

Large DNL dominantly occurs at mid-code and due to ALL resistors switching together Can unary cell bundling be regrouped to reduce DNL

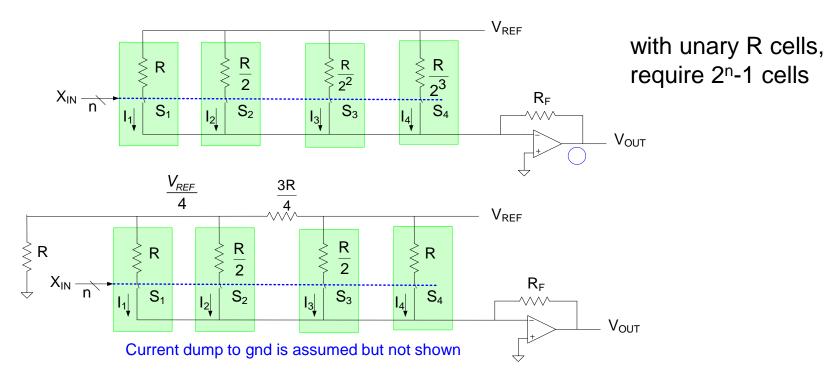

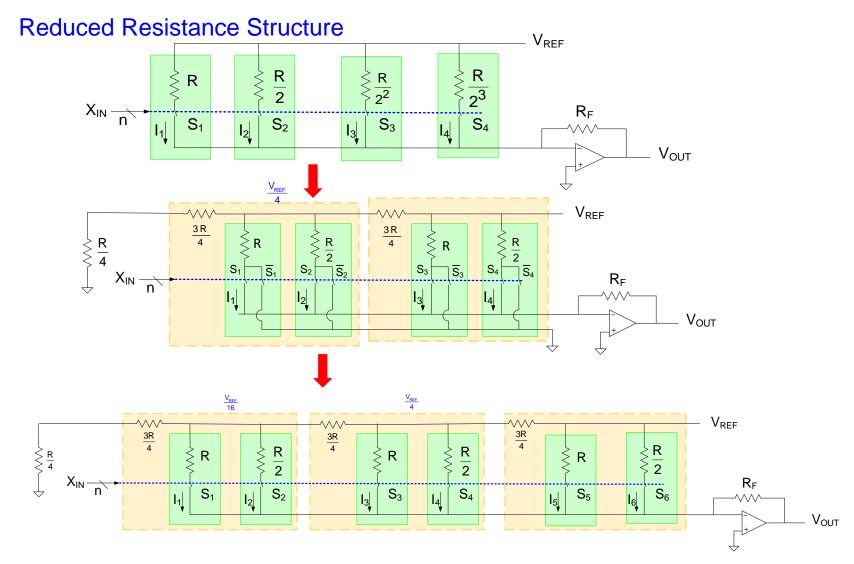

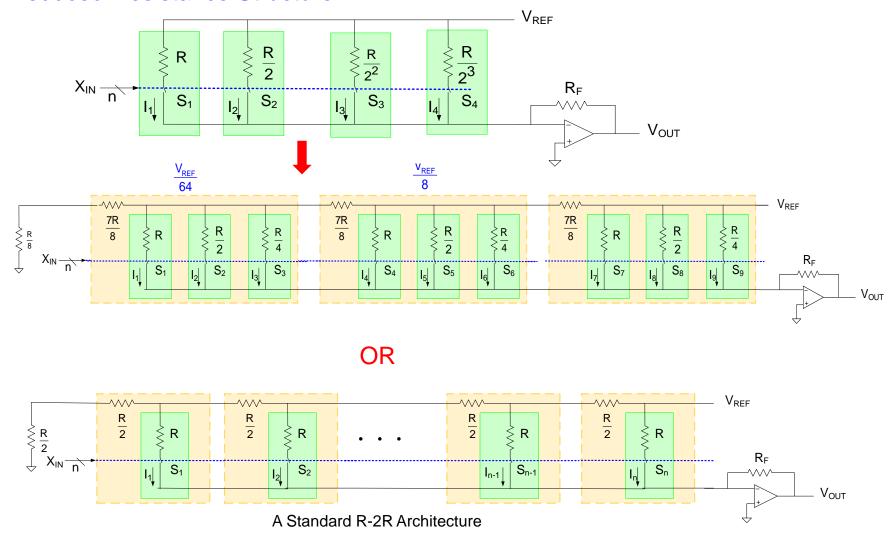

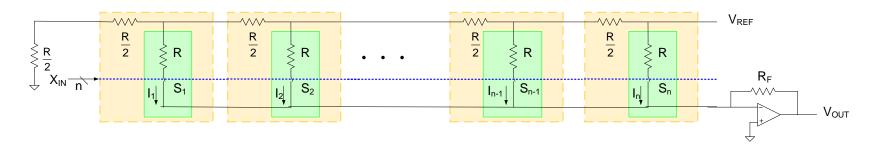

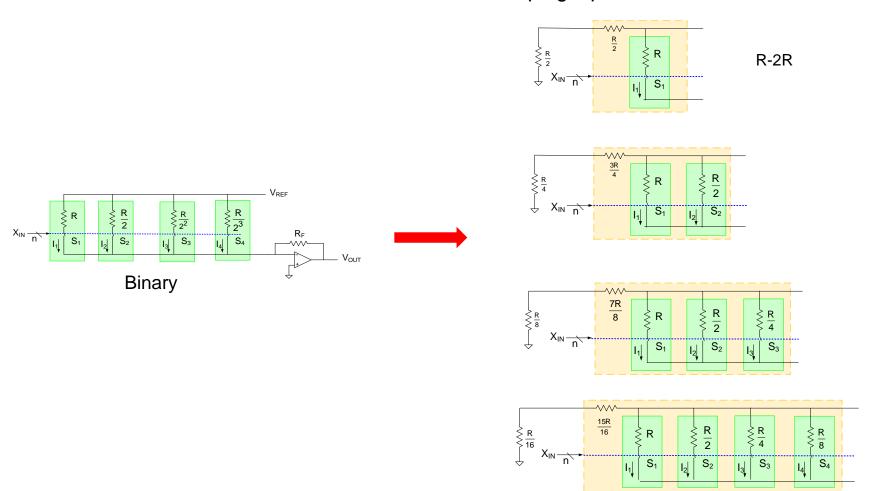

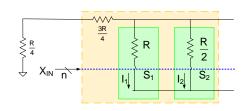

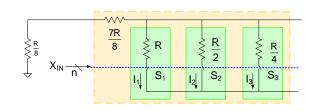

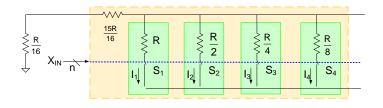

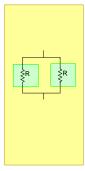

#### Reduced Resistance Structure

(actually concerned about number of unary cells, not total ohmic resistance)

- Significant reduction in resistance possible

- Can be inserted at more than one place to further reduce resistance values

- Introduces a "floating node" but voltage on floating node does not change (if current is stee

- Current drawn from V<sub>RFF</sub> does not change with code

- Dummy switching can be used for β compensation

- If inserted at each intersection becomes R-2R structure

#### Reduced Resistance Structure

with unary R/2 cells, required 3n+1 cells compared to 2<sup>n</sup>-1 cells for binary bundled array

#### Reduced Resistance Structure

3n+1 cells

Is the R-2R structure smaller?

Does the R-2R structure perform better?

What metric should be used for comparing performance?

Reduced Resistance Structure

Slice Grouping Options with Series Resistors

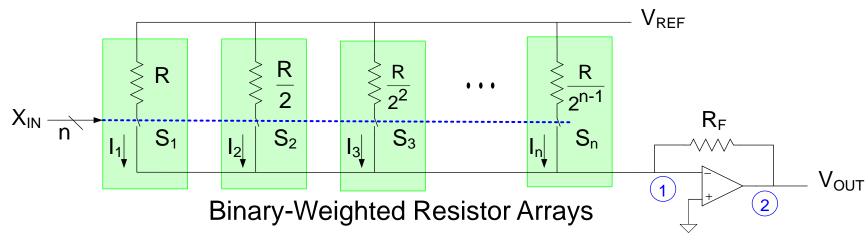

Binary-Weighted Resistor Arrays

Actual layout of resistors is very important

#### Performance of Thermometer Coded vs Binary Coded DACs

#### Conventional Wisdom:

- Thermometer-coded structures have inherently small DNL

- Binary coded structures can have large DNL

- INL of both structures is comparable for same total area (provided area appropriately allocated)

- Will consider String DAC but nearly same results for current-steering DACs

- Current Steering DAC will generate current from resistors

- ➤ For Binary Coded DAC, MSB: 2<sup>n-1</sup> unary cells in parallel .... LSB: single unary cell

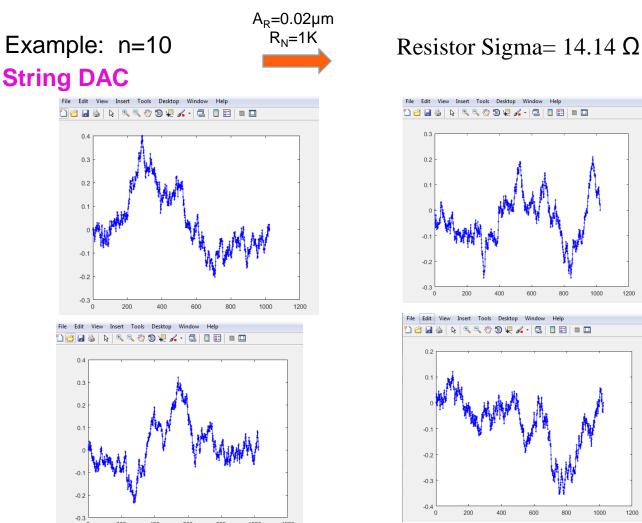

- Consider unit resistor of area 2µm² (shape not critical)

- Matching parameter A<sub>R</sub>=0.02μm

- R<sub>N</sub>=1K (not critical)

$$\sigma_R = \frac{R_N}{\sqrt{A}} A_{\rho R}$$

Assume Gaussian Distribution of Resistors

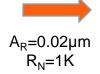

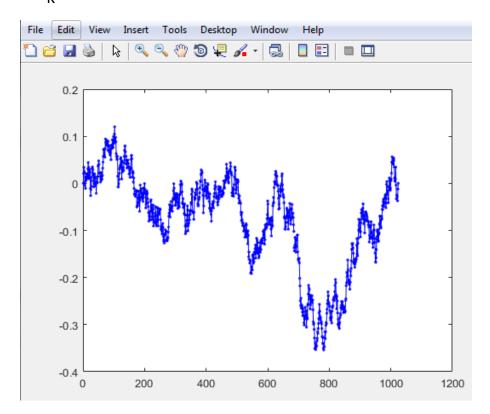

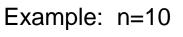

Example: n=10

A<sub>p</sub>=0.02um

Resistor Sigma=  $14.14 \Omega$

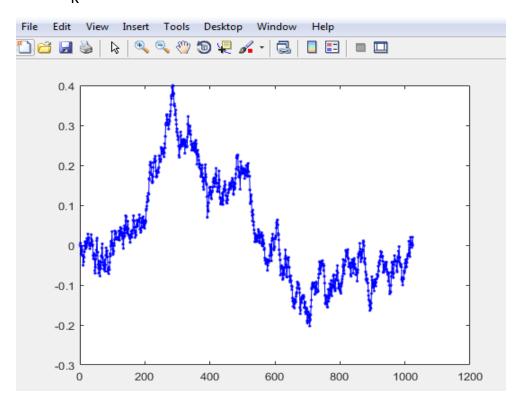

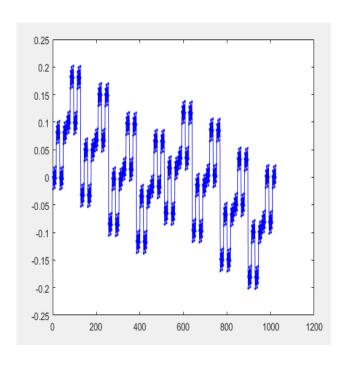

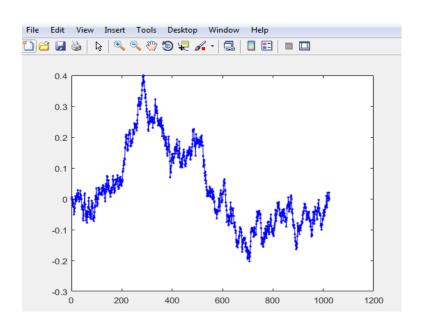

**String DAC**

A<sub>R</sub>=0.02μm R<sub>N</sub>=1K

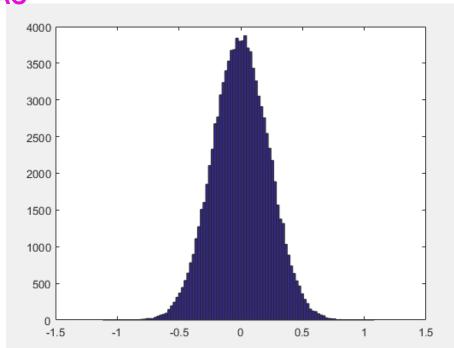

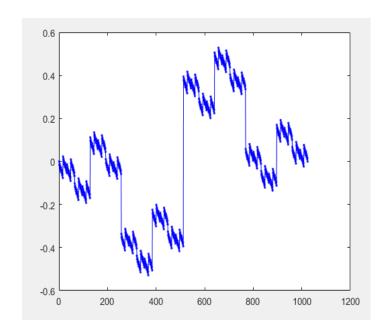

Simulation 1: INL<sub>k</sub>

Example: n=10

**String DAC**

Resistor Sigma=  $14.14 \Omega$

Simulation 2: INL<sub>k</sub>

Example: n=10

**String DAC**

Resistor Sigma=  $14.14 \Omega$

Simulation 3: INL<sub>k</sub>

Example: n=10

**String DAC**

Resistor Sigma=  $14.14 \Omega$

Simulation 4: INL<sub>k</sub>

Low DNL and random walk nature should be apparent

Resistor Sigma=  $14.14 \Omega$

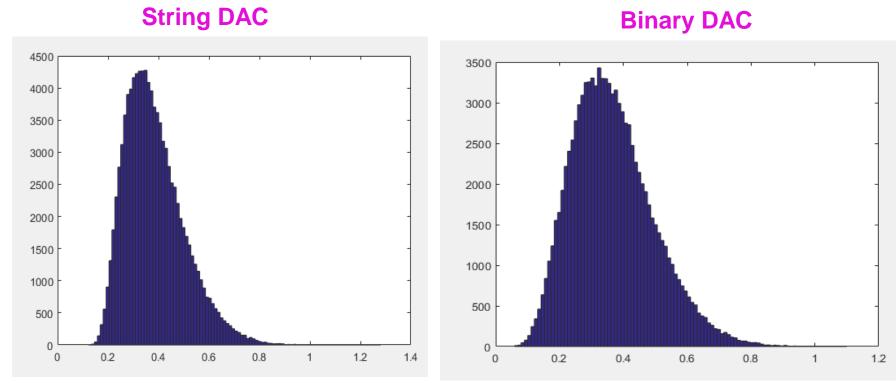

**String DAC**

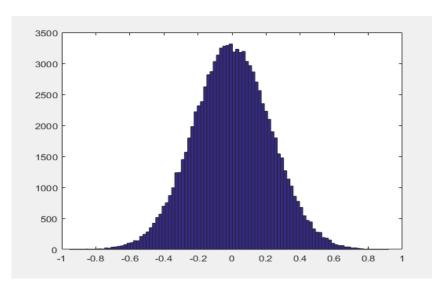

INLkmax\_mean = -2.11116e-05 INLkmax\_sigma = 0.226783

Histogram of INL<sub>kmax</sub> from 100,000 runs

Appears to be Gaussian

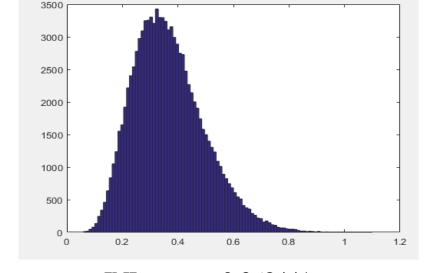

Histogram of INL from 100,000 runs

Not Gaussian

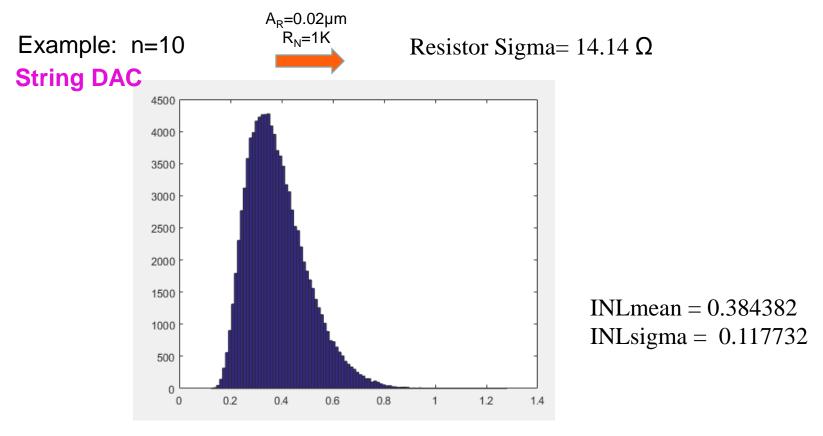

Example: n=10

R<sub>N</sub>=1K

$A_{p} = 0.02 \mu m$

Resistor Sigma=  $14.14 \Omega$

**String DAC**

Histogram of INL from 100,000 runs

INLkmax\_mean = -2.11116e-05 INLkmax\_sigma = 0.226783 Gaussian (and analytical)

INLmean = 0.384382 INLsigma = 0.117732 Not Gaussian

Question: Can a predictor of JNL be obtained from INLkmax?

$$\sigma_{INL} = \phi(\sigma_{INLkmax}, A_R, A, n)$$

Question: Can a predictor of f<sub>INL</sub> (the pdf) be obtained from f<sub>INLkmax</sub>?

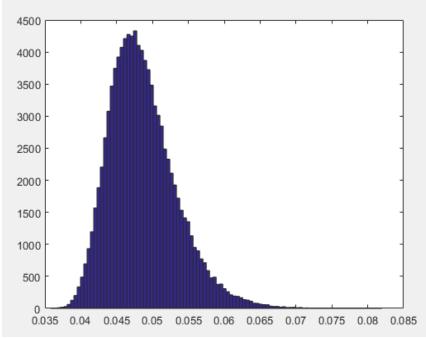

Example: n=10

$A_R=0.02\mu m$   $R_N=1K$

Resistor Sigma=  $14.14 \Omega$

String DAC

DNLmean = 0.0486494 DNLsigma = 0.00471025

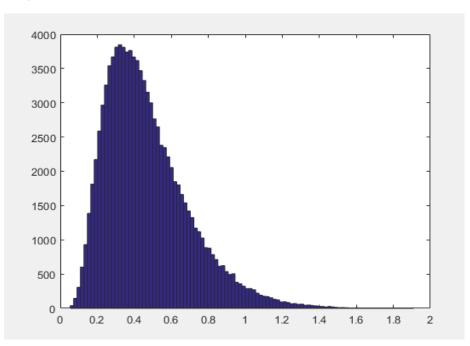

Histogram of DNL from 100,000 runs

Not Gaussian but both mean and sigma are very small

Question: Can a predictor of f<sub>DNL</sub> (the pdf) be obtained from f<sub>INL</sub>?

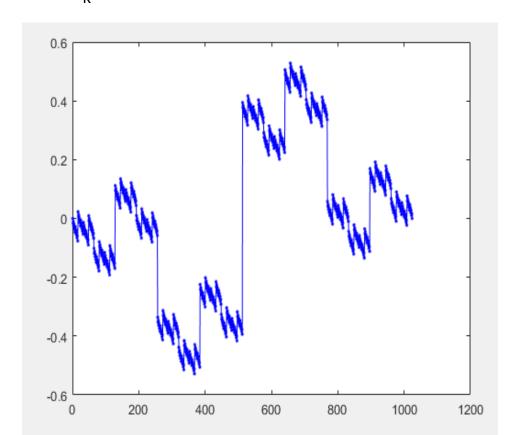

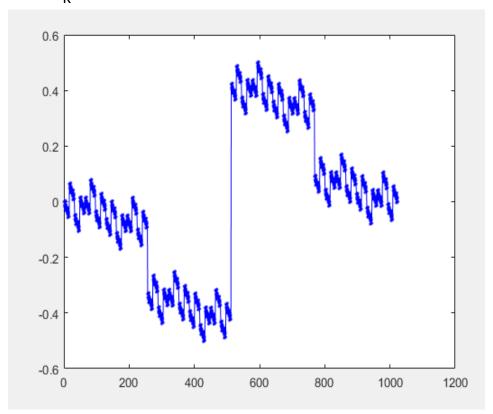

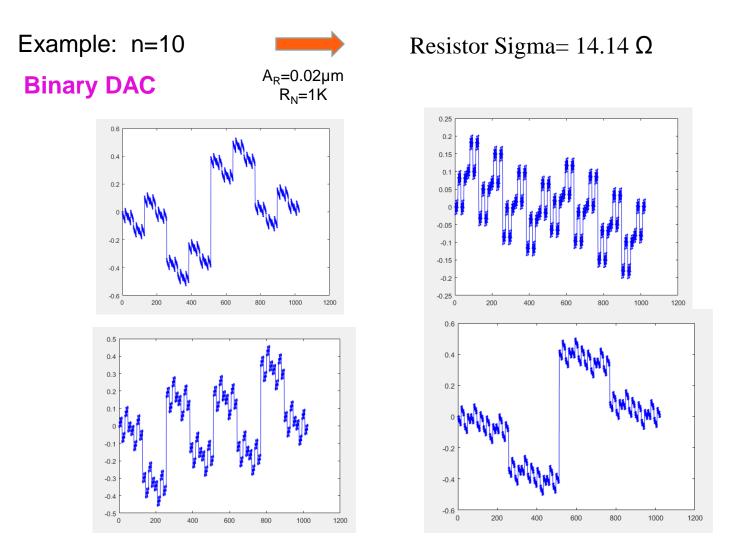

Example: n=10

0.02um

Resistor Sigma=  $14.14 \Omega$

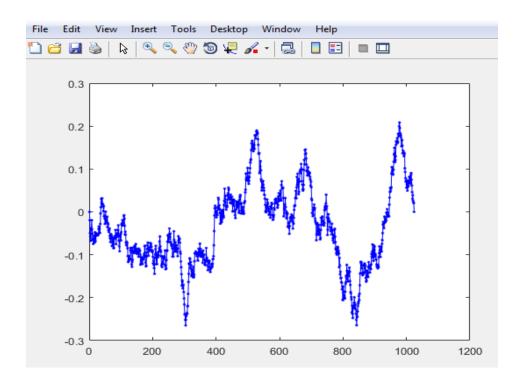

**Binary DAC**

A<sub>R</sub>=0.02μm R<sub>N</sub>=1K

Simulation 1: INL<sub>k</sub>

Example: n=10

A<sub>R</sub>=0.02μm

$R_N=1K$

Resistor Sigma=  $14.14 \Omega$

**Binary DAC**

Simulation 2: INL<sub>k</sub>

Example: n=10

A<sub>R</sub>=0.02μm

$R_N=1K$

Resistor Sigma=  $14.14 \Omega$

**Binary DAC**

Simulation 3: INL<sub>k</sub>

Example: n=10

0.02um

Resistor Sigma=  $14.14 \Omega$

**Binary DAC**

$A_R=0.02\mu m$  $R_N=1K$

Simulation 4: INL<sub>k</sub>

Large DNL bit INL does not appear to be much different than for string DAC

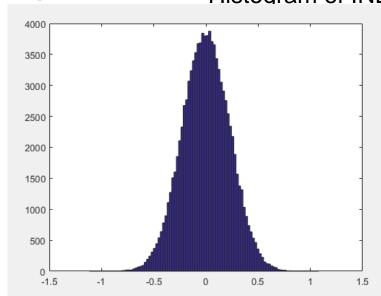

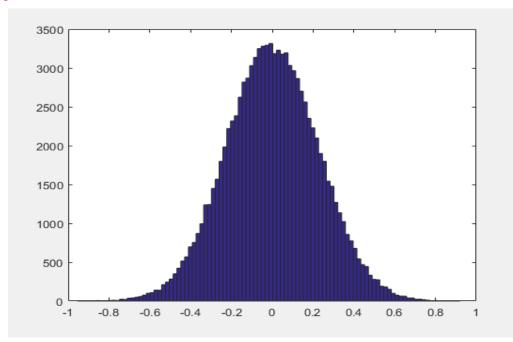

Example: n=10

Resistor Sigma=  $14.14 \Omega$

#### **Binary DAC**

INLkmax\_mean = -.00526008 INLkmax\_sigma = 0.23196

Histogram of INL<sub>kmax</sub> from 100,000 runs

Appears to be Gaussian

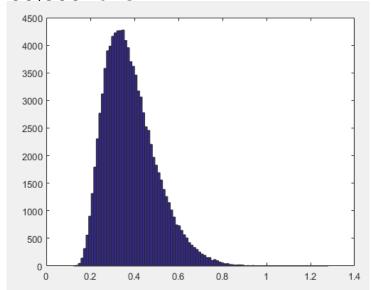

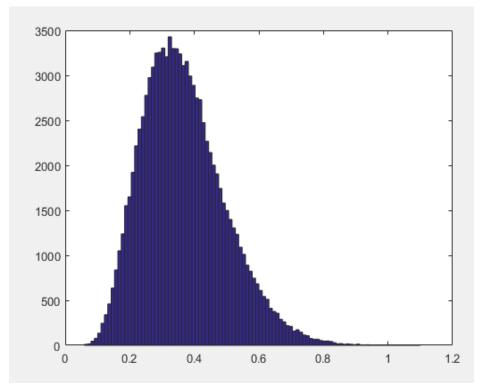

Example: n=10

$A_R=0.02\mu m$   $R_N=1K$

Resistor Sigma=  $14.14 \Omega$

#### **Binary DAC**

INLmean = 0.368441 INLsigma = 0.126133

Histogram of INL from 100,000 runs

Not Gaussian

Example: n=10

$A_R=0.02\mu m$   $R_N=1K$

Resistor Sigma=  $14.14 \Omega$

**Binary DAC**

Histogram of INL from 100,000 runs

INLkmax\_mean = -.00526008 INLkmax\_sigma = 0.23196

Gaussian (and analytical)

INLmean = 0.368441INLsigma = 0.126133

Not Gaussian

Question: Can a predictor of INL be obtained from INLkmax?

$$\sigma_{INL} = \phi(\sigma_{INLk\max}, A_R, A, n)$$

Question: Can a predictor of f<sub>INL</sub> (the pdf) be obtained from f<sub>INLkmax</sub>?

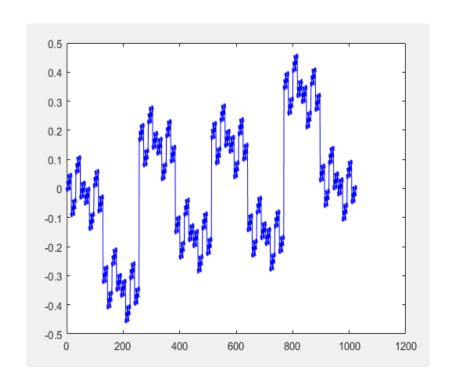

Example: n=10

**Binary DAC**

Resistor Sigma=  $14.14 \Omega$

DNLmean = 0.46978 DNLsigma = 0.227768

Histogram of DNL from 100,000 runs

Not Gaussian and both mean and sigma are not small

Question: Can a predictor of  $f_{DNL}$  (the pdf) be obtained from  $f_{INL}$ ?

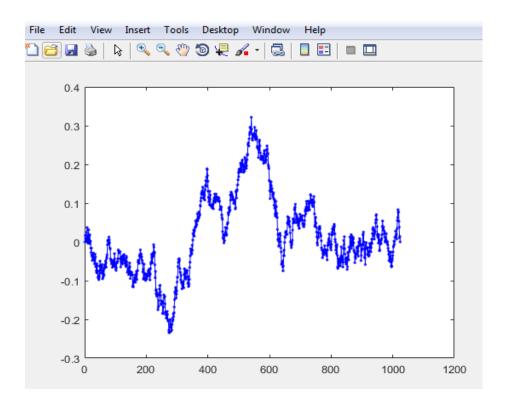

Example: n=10

Resistor Sigma=  $14.14 \Omega$

Simulation 1: INL<sub>k</sub>

String

**Binary Weighted**

Actual outputs will differ significantly

Example: n=10

Resistor Sigma=  $14.14 \Omega$

Both structures have essentially the same area

Histogram of INL from 100,000 runs

Since mathematical form for PDF is not available, not easy to analytically calculate yield

Example: n=10

$$A_R=0.02\mu m$$

$R_N=1K$

Resistor Sigma=  $14.14 \Omega$

Both structures have essentially the same area

#### String DAC

Resolution = 10 AR = 0.02

Rnom = 1000 Area Unit Resistor =  $2\mu m^2$

$INLkmax_mean = -2.11116e-05$

INLmean € 0.384382

INLtarget = 0.5000

Nruns = 100000

Resistor Sigma= 14.1421

INLkmax sigma = 0.226783

INLsigma = 0.117732

Yield(%) = 84.0120

#### **Binary DAC**

Resolution = 10 AR = 0.02

Rnom = 1000 Area unit resistor= $2\mu m^2$

INLmean = 0.367036

INLkmax mean = 0.000130823

$\frac{DNLmean}{DNLtarget} = 0.46978$   $\frac{DNLtarget}{DNLtarget} = 0.5000$

Nruns = 100,000

Resistor Sigma= 14.1421

INLsigma = 0.128294

INLkmax sigma = 0.226276

DNLsigma = 0.227768Yield (%) = 84.8580

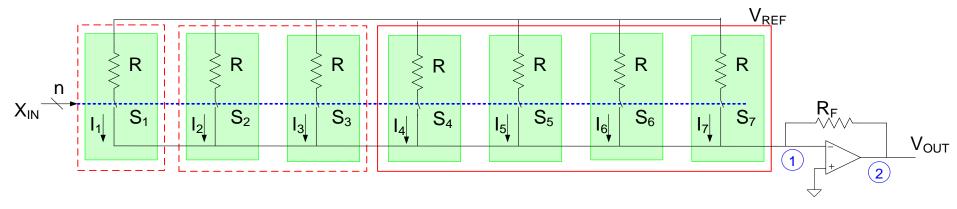

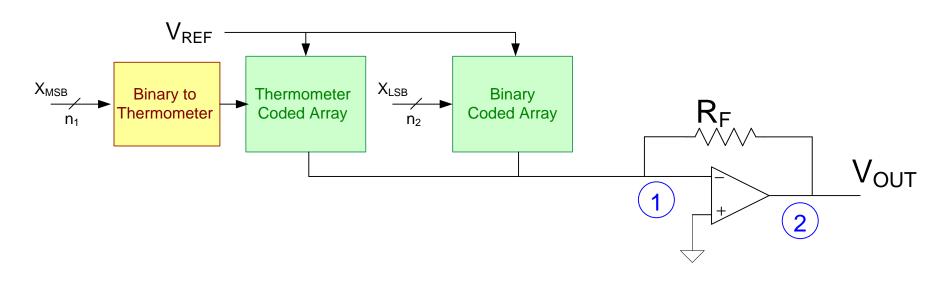

#### Current Steering DACs

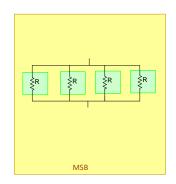

#### Segmented Resistor Arrays

- Combines two types of architectures

- Can inherit advantages of both thermometer and binary approach

- Minimizes limitations of both thermometer and binary approach

#### Current Steering DACs

#### Reduced Resistance Structure

#### Slice Grouping Options with Series Resistors

Is it better to use series unary cells to form R or parallel unary cells to form  $\frac{R}{2^n}$ ?

In the two scenarios, is the dominant area allocated to the MSB or the LSB part of the ladder?

Will this choice make much difference in yield?

What yield-related performance metric will be most affected?

#### Current Steering DACs

#### Reduced Resistance Structure

Is it better to use series unary cells to form R or parallel unary cells to form  $\frac{R}{2^n}$ ?

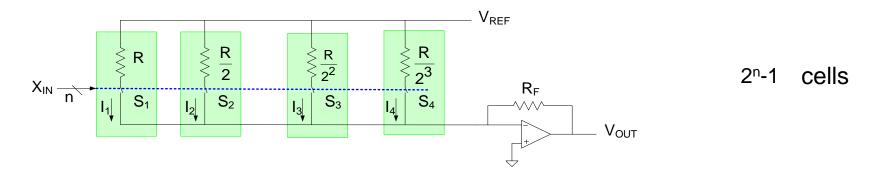

2<sup>n</sup>-1 cells

for n odd  $2^{\frac{n+3}{2}} - 3$  cells

2<sup>n</sup>-1 cells

| n  | Series | Parallel | Split |

|----|--------|----------|-------|

| 3  | 7      | 7        | 5     |

| 5  | 31     | 31       | 13    |

| 7  | 127    | 127      | 29    |

| 9  | 511    | 511      | 61    |

| 11 | 2047   | 2047     | 125   |

| 13 | 8191   | 8191     | 253   |

| 15 | 32767  | 32767    | 509   |

Stay Safe and Stay Healthy!

#### End of Lecture 16